пока не знаю. Надо пробовать. Я над этим-то решением две ночи просидел ![]()

Таймеры АВР не приспособлены под одиночные импульсы, таймер выходит на режим только на втором цикле после запуска. Как все это инициализируется на первом цикле - в даташите не описано.

Я завтра на свежую голову посижу с ICR1 если дадут, первоначальная инициализация и случайные импульсы при этом нормально ![]()

Если с ICR1 не удастся, сделаю временно тогда с wgm15 и OCR1A, пускай нужно будет давать лишний стоповый что бы обновить.

А потом может Stm32 придёт, буду с ними разбираться… ![]()

Можно ещё раз описать задачу? Без таймеров и прочего железа. Что имеем и что должны получить? Откуда импульсы на внешних ногах или их сами генерим? Задержка между импульсами постоянная или можно задавать? Сами импульсы нормируются или примерно сотня нан? Время между импульсами это время между фронтами или между концом первого и началом второго? Диаграмму бы хоть от руки. Перечитал всю тему, но ответов нет.

Та часть задачи, которая не получается это: 1)генерация двух отрицательных импульсов на разных ногах ардуино нано длительностью 2 такта каждый

2) задержка между ними должна регулироваться с точностью 1такт. Задержка считается между передними фронтами

3) задержка от 3 до 35мкс

То есть выставил длительность 12 микросекунд к примеру и чтобы была возможность уменьшить или увеличить задержку между ними на нужное количество тактов.

Потом выставил 20 микросекунд и то же самое и так далее.

Там ещё много всего(подача 3его сигнала перед этими двумя, подача только 3его и 1ого, 3его и 2го, но в этих случаях точность не важна и вроде так все решаемо, изменение длительности 2ого сигнала и прочее) но это все просто и решаемо

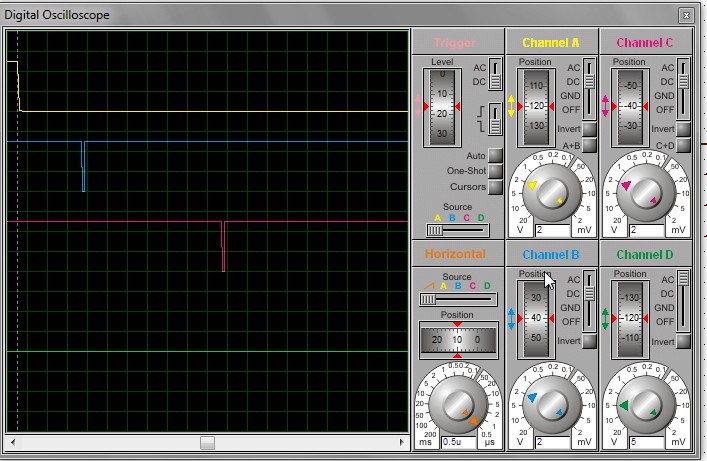

а при включении ноги должны быть в нуле? у меня получилось двумя таймерами, выход OC0B → на вход T1.

Но срабатывает одни раз, т е два импульса нуля, между ними длинная единичка, циклически не могу повторить ![]() где то косяк.

где то косяк.

Если нужно всего два импульса, то задача облегчается.

а зачем на разных ногах МК одинаковые импульсы? что мешает с одного пина снимать на два устройства.

Evgeniy, а у меня разве не так? Я только регулировку не делал.

2 канала нужны, по тому, что далее два независимых 2 усилителя с разным уровнем по выходу после.

Состояние пинов при работе - высокий уровень, а отрицательными импульсами заставляет сработать усилитель. Железная часть именно под это собрана, то есть под отрицательный импульс. Скоро надеюсь придут микросхемы, которые должны от положительного сработать, но это для теста заказывалось и фронты судя по даташиту будут слишком долгими. В общем пока работаем с тем что есть ![]()

Прошу прощения, признаюсь, что видел, но не анализировал код, очень много информации со всех сторон. Тружусь над этим в перерывах между основной работой.

Зациклился на допиливании своего кода, так как осталась вроде бы мелочь и решений от b707.

В общем пойду изучать. Спасибо

Мне кажется, что тут так же упрется в то, что обновлять OCR1A нельзя во время остановленного таймера, оно обновится только на следующий такт после того как TCNT1 =OCR1A

судя по “When the OCR1A I/O location is written the

value written will be put into the OCR1A buffer register. The OCR1A compare register will then be updated with the value in

the buffer register at the next timer clock cycle the TCNT1 matches TOP”

Может есть какой то адрес, куда можно сразу записать это значение? Либо опять искать решение в ICR1, другом методе(например ассемблер, но туда лезть совсем не хочется) или stm32 ![]()

Хотя в голову пришло, что можно наверное обнулять TCCRA и TCCRB полностью каждый раз и по новой задавать все значения. Завтра проверю

Я ж просил без железа. Длительность какая нужна? У разных МК такты могут быть разные.

Запуск цикла чем? После первого запуска повторять цикл надо?

Длительность ~100наносекунд, точно не вспомню сейчас цифры, надо смотреть бумаги, но у одного вроде до 200нс, у другого до 150нс.

в случае использования двух каналов compare match это как раз не проблема, так как второй импульс всегда подается после перехода таймера через TOP и обновления длительности задержки между импульсами.

попробуйте, у меня не вышло. Если задавать все регистры по новой - вы опять будете иметь паразитные выбросы по кналам при старте

Там получается так, что не знаешь какая следующая тебе задержка потребуется. То есть отработало одно значение, а при следующем нажатии может потребоваться любое другое значение, это только ясно когда посмттрел на результат. Или же тоже самое но с поправкой на пару тактов в ту или другую сторону.

Можно в виде костыля просто подавать одиночный стоп сигнал для обновления импульса, пока идут стм32,а потом уже переделать на ней.

о наверняка же есть какой то системный адрес OCR1A куда можно записать значение? Гугл не выдал ничего по этому вопросу

а даташит? это последние страницы обычно

Offset Name Bit Pos.

0x86 ICR1L 7:0 ICRL[7:0]

0x87 ICR1H 7:0 ICRH[7:0]

0x88 OCR1AL 7:0 OCRAL[7:0]

0x89 OCR1AH 7:0 OCRAH[7:0]

0x8A OCR1BL 7:0 OCRBL[7:0]

0x8B OCR1BH 7:0 OCRBH[7:0

Задавать ОCR1A, OCR1B cразу после старта.

void loop() {

if (get_key(KEY_START)) {

TCNT1 = 0;

start_pulse();

start_timer();

//задаём новые значения OCR1A и OCR1B (на 1 меньше)

delay(500);

}

}

Я о том и говорю, что это не проблема.

В моем коде в КАЖДОЙ ПАРЕ сигналов первый сигнал идет ДО переполнения таймера, а второй ПОСЛЕ. То есть значение задержки между ними автоматически получается обновленным, и ни в какие секретные регистры его для этого записывать не надо.

В отличии от этого в вашем коде значение TOP обновляется уже ПОСЛЕ подачи второго сигнала, отсюда и проблемы.

А, ну да, как у меня обновление не прокатит.(

Наверное это единственный вариант на таймерах, который будет без костылей. Завтра подумаю как переделать это на постоянные A>B…A>B… итд